#### **General Description**

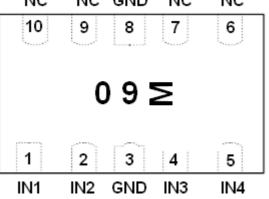

The AFE099P is a 4-channel ultra low capacitance rail clamp ESD protection diodes array. Each channel consists of a pair of ESD diodes that steer positive or negative ESD current to either the positive or negative rail.

A zener diode is integrated in to the array between the positive and negative supply rails. In the typical applications, the negative rail pin (assigned as GND) is connected with system ground. The Positive ESD current is steered to the ground through an ESD diode and Zener diode and the positive ESD voltage is clamped to the zener voltage.

The AFE099P is idea to protect high speed data lines.

#### Features

- 4 channels of ESD protection

- Provides ESD protection to IEC61000-4-2 level 4 ±17 KV air discharge

- ±12 KV contact discharge

- Channel I/O to GND capacitance: 0.9pF(Max)

- Channel I/O to I/O capacitance: 0.45pF(Max)

- Low clamping voltage

- 5V low operating voltage

- Improved Zener structure

- Optimized package for easy high speed data lines PCB layout

- ROHS compliant

#### Application

- High Definition Multi-Media Interface Protection

- USB 3.0 Power and Data Line Protection

- Monitors and Flat Panel Displays Notebook Computers

- Video Line Protection & Base Stations

- HDSL, IDSL Secondary IC Side Protection

- Microcontroller Input Protection

- LCD and camera modules

- 10/100/1000 Ethernet

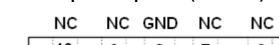

Pin Description Top View (DFN-10)

#### **Ordering Information**

| Part Ordering No. | Part Marking | Package | Unit        | Quantity |

|-------------------|--------------|---------|-------------|----------|

| AFE099PFN10RG     | 09M          | DFN-10  | Tape & Reel | 3000 EA  |

% 09 Specific Device Code

M Month Code

X AFE099PFN10RG : 7" Tape & Reel ; Pb- Free ; Halogen- Free

©Alfa-MOS Technology Corp.

### ABSOULTE MAXIMUM RATINGS

(T<sub>A</sub>=25 $^{\circ}$ C Unless otherwise noted)

| Parameter                                   | Symbol          | Typical   | Unit |

|---------------------------------------------|-----------------|-----------|------|

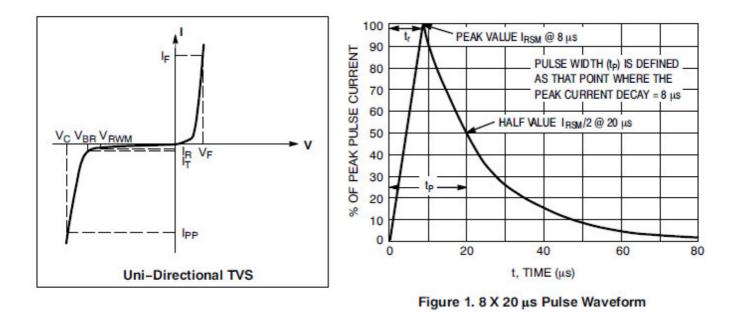

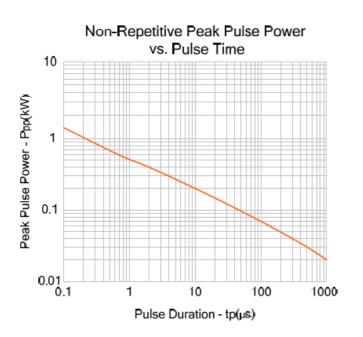

| Peak Pulse Power ( tp = 8/20 µs )           | P <sub>pk</sub> | 150       | W    |

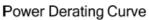

| Peak Pulse Current ( $t_p = 8/20 \ \mu s$ ) | PP              | 5         | A    |

| ESD per IEC 61000 – 4 – 2 (Air )            | Vesd1           | ±17       | KV   |

| ESD per IEC 61000 – 4 – 2 (Contact )        | Vesd2           | ±12       | KV   |

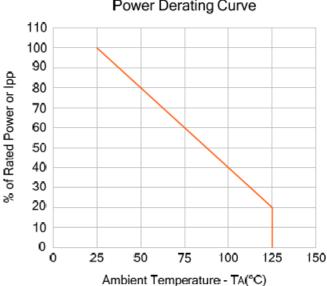

| Operating Junction Temperature              | TJ              | -55 ~ 125 | °C   |

| Storage Temperature Range                   | Tstg            | -55 ~ 150 | °C   |

### **ELECTRICAL CHARACTERISTICS**

(TA=25°C Unless otherwise noted)

| Parameter                                  | Symbol          | Conditions                                                  | Min. | Тур  | Max. | Unit |

|--------------------------------------------|-----------------|-------------------------------------------------------------|------|------|------|------|

| Reverse Working Voltage                    | VRWM            | Any Pin to GND                                              |      |      | 5    | V    |

| Reverse Breakdown Voltage                  | VBR             | It = 1mA<br>Any Pin to GND                                  | 6    |      |      | V    |

| Reverse Leakage Current                    | IR              | V <sub>RWM</sub> = 5V , T=25℃<br>Any Pin to GND             |      |      | 1    | μA   |

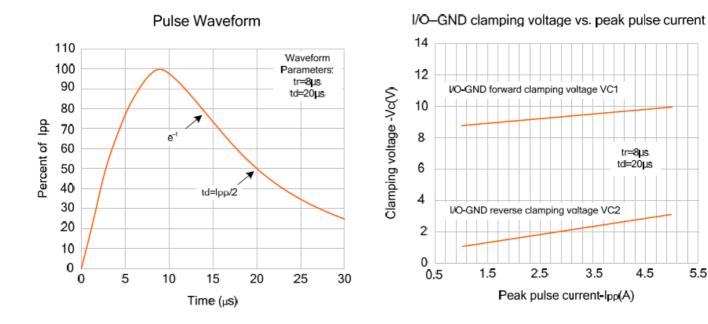

| Positive Clamping Voltage                  | V <sub>C1</sub> | IPP = 1A , tp = 8/20 µs<br>Positive pulse<br>Any Pin to GND |      | 8.5  | 12   | V    |

| Negative Clamping Voltage                  | V <sub>C2</sub> | IPP = 1A , tp = 8/20 µs<br>Negative pulse<br>Any Pin to GND |      | 1.8  |      | V    |

| Junction Capacitance<br>Between Channel    | Cj1             | V <sub>R</sub> = 0V , f = 1MHz<br>Between I/O Pin           |      | 0.35 | 0.45 | pF   |

| Junction Capacitance<br>Between I/O to GND | Cj2             | V <sub>R</sub> = 0V , f = 1MHz<br>Any Pin to GND            |      |      | 0.9  | pF   |

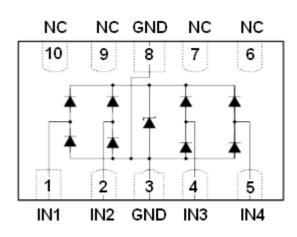

### **Electrical Parameter**

| Symbol           | Parameter                              |  |

|------------------|----------------------------------------|--|

| I <sub>PP</sub>  | Maximum Reverse Peak Pulse Current     |  |

| Vc               | Clamping Voltage @ IPP                 |  |

| V <sub>RWM</sub> | Working Peak Reverse Voltage           |  |

| I <sub>R</sub>   | Maximum Reverse Leakage Current @ VRWM |  |

| IT               | Test Current                           |  |

| V <sub>BR</sub>  | Breakdown Voltage @ IT                 |  |

| I <sub>F</sub>   | Forward Current                        |  |

| VF               | Forward Voltage @ IF                   |  |

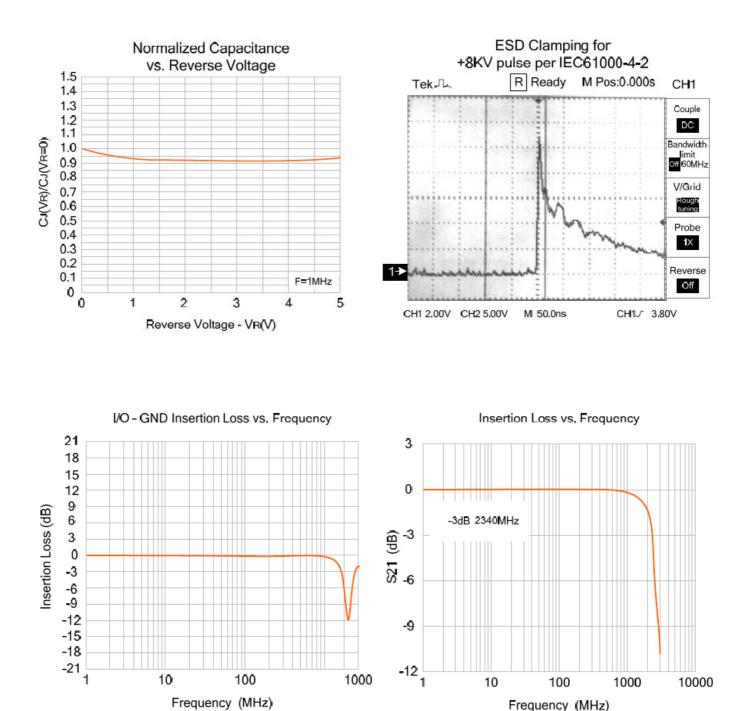

### **Typical Characteristics**

### **Typical Characteristics**

©Alfa-MOS Technology Corp. Rev.A May 2013

### **Schematic & Pin Configuration**

As Figure Shown is an example of how to route the high speed differential traces through the AFE099P.The solid line represents the PCB trace. The PCB traces are used to connect the pin pairs for each line (pin 1 to pin 10, pin 2 to pin 9, pin 4 to pin 7, pin 5 to pin 6). For example, line 1 enters at pin 1 and exits at Pin 10 and the PCB trace connects pin 1 and 10 together. This is true for lines connected at pins2, 4, and 5 also. Ground is connected at pins3 and 8. One large ground pad should be used in lieu of two separate pads.

Flow through Layout Using AFE099P

### Application Information (Design Recommendations for HDMI Protection)

Adding external ESD protection to HDMI ports can be challenging. First, ESD protection devices have an inherent junction capacitance. However, adding even a small amount of capacitance will cause the impedance of the differential pair to drop. Second , large packages and land pattern requirements cause discontinuities that adversely affect signal integrity. The AFE099P and is specifically designed for protection of high-speed interfaces such as HDMI. They present <0.45pF capacitance between the pairs while being rated to handle +/-12KV ESD contact discharges (17KVair discharge) as outlined in IEC61000-4-2. Each device is in a leadless DFN package that is less than 1.1mm wide. They are designed such that the traces flow straight through the device. The narrow package and flow-through design reduces discontinuities and minimizes impact on signal integrity. This becomes even more critical as signal speeds increase.

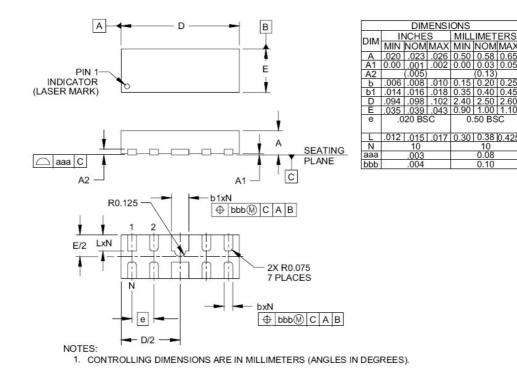

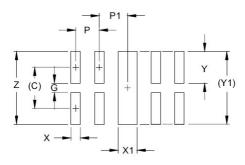

### Package Information (DFN-10)

| DIMENSIONS |        |             |  |  |

|------------|--------|-------------|--|--|

| DIM        | INCHES | MILLIMETERS |  |  |

| С          | (.034) | (0.875)     |  |  |

| G          | .008   | 0.20        |  |  |

| Р          | .020   | 0.50        |  |  |

| P1         | .020   | 0.50        |  |  |

| X          | .008   | 0.20        |  |  |

| X1         | .016   | 0.40        |  |  |

| Y          | .027   | 0.675       |  |  |

| Y1         | (.061) | (1.55)      |  |  |

| Z          | .061   | 1.55        |  |  |

#### NOTES:

1. CONTROLLING DIMENSIONS ARE IN MILLIMETERS (ANGLES IN DEGREES).

2. THIS LAND PATTERN IS FOR REFERENCE PURPOSES ONLY.

CONSULT YOUR MANUFACTURING GROUP TO ENSURE YOUR COMPANY'S MANUFACTURING GUIDELINES ARE MET.

©2010 Alfa-MOS Technology Corp. 2F, No.80, Sec.1, Cheng Kung Rd., Nan Kang Dist., Taipei City 115, Taiwan (R.O.C.) Tel : 886 2) 2651 3928 Fax : 886 2) 2786 8483 ©http://www.alfa-mos.com